# ISL91302B AND ISL91301A/B

MULTI-PHASE BUCK PMIC AND MULTI-OUTPUT, MULTI-PHASE BUCK PMIC

BIG IDEAS FOR EVERY SPACE

# ADVANTAGES OF RENESAS R5 MULTIPHASE DC/DC PRODUCTS

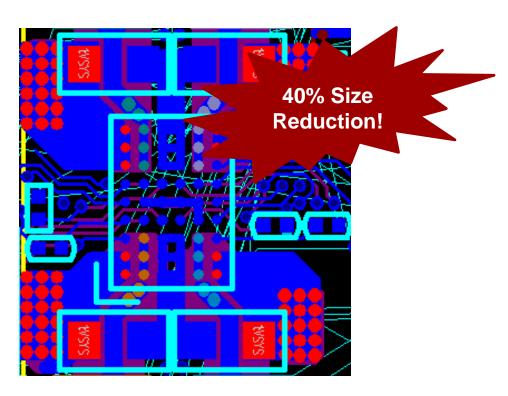

#### Small PCB size and thin solution

- 7x10mm2 total solution size for 4 outputs/phases

- Small WLCSP package

- 4MHz frequency → supports less than 2x2x1mm case size inductors

- Fast transient performance → less output capacitors

- No external components for compensation, VOUT setting, etc.

#### High efficiency

• 91% peak efficiency 3.3V → 1.0V/4A

#### Easy to design in - no PCB level design needed

- Internal compensation no need to design compensation

- Parts pre-programmed with required VOUTs, sequencing, etc.

#### Multiple package options

- WLCSP, 0.4mm pitch

- Upcoming BGA, 0.8mm pitch, samples available in early 2018 (ISL91302B)

#### Proven technology in mass production

#### TARGET MARKETS AND APPLICATIONS

#### **Industrial & Networking Markets**

- Renesas MPU and ASICs

- Industrials and FPGAs

- Enterprise Networks, Switches, Routers, WIFI

- Security and Wearable Cameras

- Optical Transceiver Modules

#### **Consumer Markets**

- Smartphones and Tablets

- SSDs

- VR / AR Goggles and Glasses

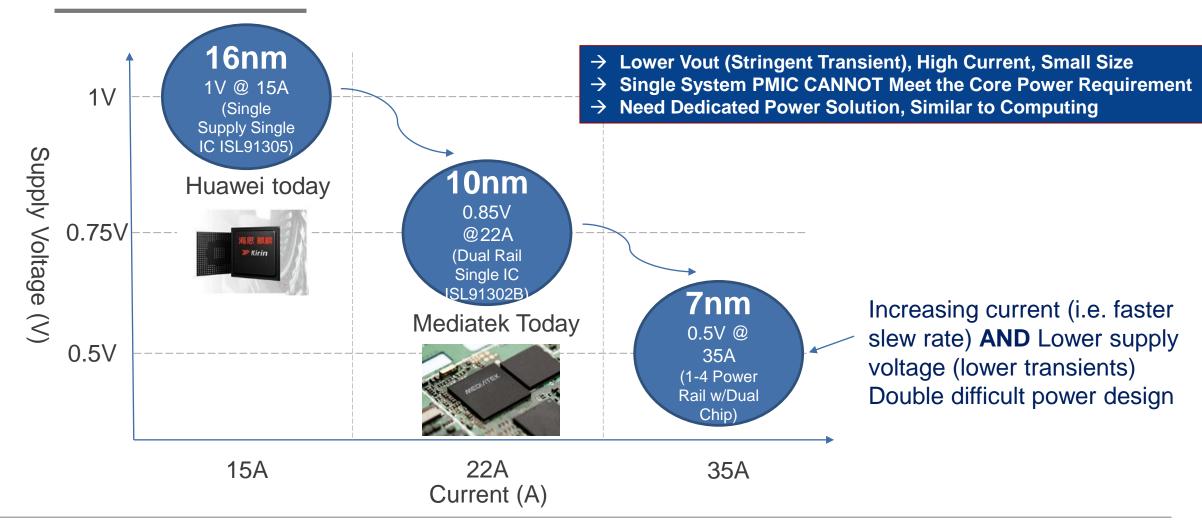

# AP PROCESS NODE TRANSITION DRIVES POWER DESIGN DEVELOPMENT

#### **CORE POWER: SMARTPHONE/TABLET VS. LAPTOP**

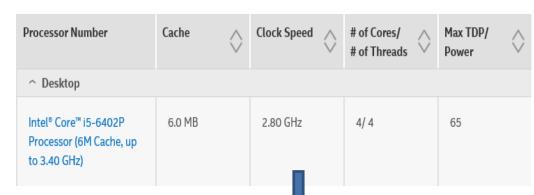

### Typical Notebook MB with Intel Core I5

SE15

**Quad-Core-CPU**

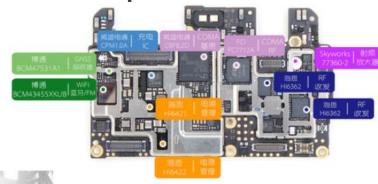

## **Huawei Latest P9 Smartphone MB**

Octa-Core-AP

| PLATFORM | OS        | Android OS, v6.0 (Marshmallow)                                 |

|----------|-----------|----------------------------------------------------------------|

|          | Chipset   | HiSilicon Kirin 955                                            |

|          | CPU       | Quad-core 2.5 GHz Cortex-A72 & quad-core 1.8 GHz Cortex-A53    |

|          | GPU       | Mali-T880 MP4                                                  |

| MEMORY   | Card slot | microSD, up to 256 GB (uses SIM 2 slot)                        |

|          | Internal  | 32 GB, 3 GB RAM (EVA-L19/EVA-L09)<br>64 GB, 4 GB RAM (EVA-L29) |

Phone AP/GPUs: Dedicated 'Sub' PMIC

→ Renesas Multi-phase Buck

#### SMARTPHONE/TABLET CORE POWER REQUIREMENT

- Smartphone/Tablet Core Power Management 'Old Socket' but now has new requirements:

- High current demanding (~ 4A 5A/phase) → 'Sub' PMIC

- Low profile solution (<=1mm)</li>

- Small footprint solution with minimum external components

- Wide input voltage range

- Low quiescent current

- High efficiency

- Tight transient spec

- Dynamic output voltage change

- Communications with AP/GPU

- Protection

#### Renesas Multi-Phase Buck:

- Dedicated voltage regulator for AP/GPUs

- It targets high performance and high current market segments

#### **ISL91302B MULTI-PHASE BUCK PMIC**

Designed to meet the stringent AP/GPU applications:

- Small solution size

- High output current capability

- Flexible configuration through internal one time programmable (OTP) registers

- Best efficiency performance

- Best transient response with proprietary R5 control technique

- Accurate system level telemetry ADC for VIN, Vout, IOUT, temperature, etc.

- Support I<sup>2</sup>C and SPI communication protocol

- Full protection features, e.g., OV, UV, OT, OC

ISL91302B Solution Size: 70 mm<sup>2</sup>

# PRODUCT HIGHLIGHTS ISL91302B AND ISL91301A/B

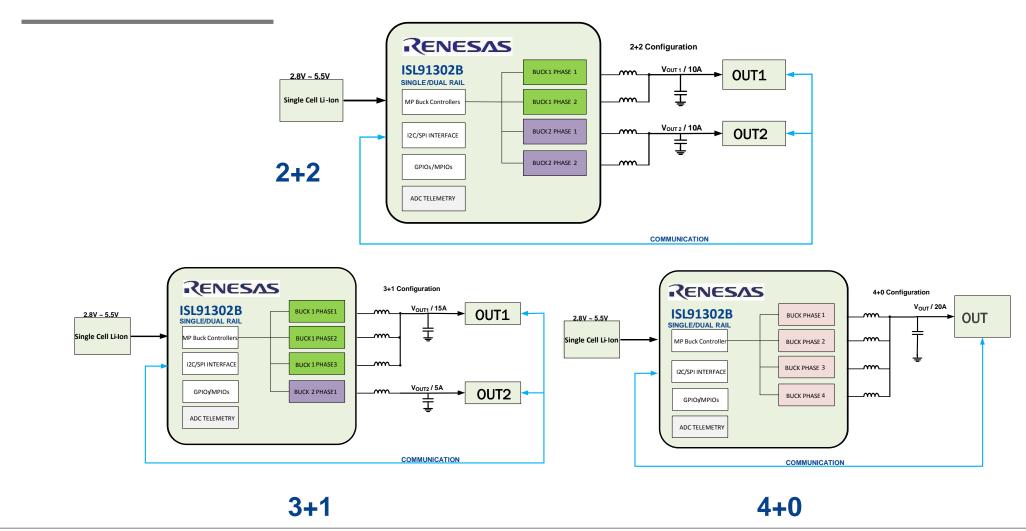

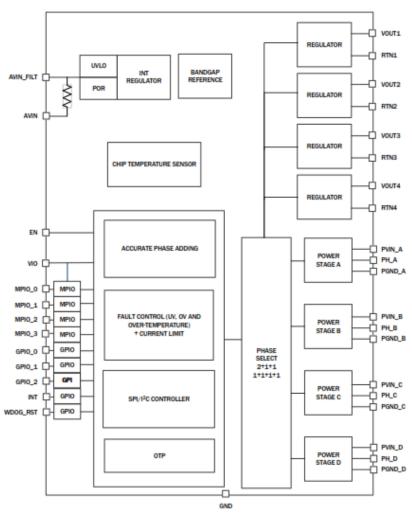

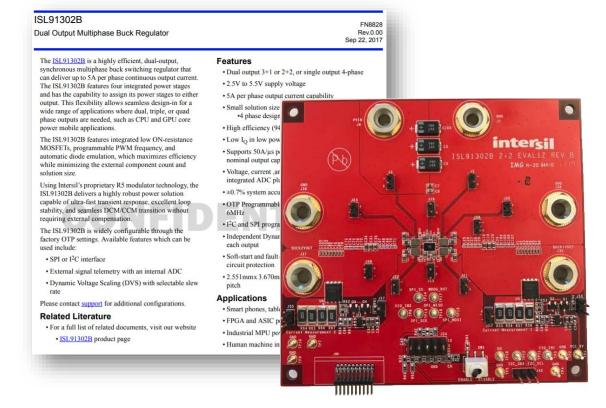

#### ISL91302B: MULTI-OUTPUT MULTI-PHASE BUCK PMIC

#### ISL91302B: MULTI-OUTPUT MULTI-PHASE BUCK PMIC

#### ISL91302B

- Supported output configurations

- Dual phase: 2+2; Max output: 10A+10A

- Triple phase: 3+1, Max output: 15A + 5A

- Quad phase: 4+0, Max output: 20A

- 2.5V to 5.5V supply voltage

- Programmable output from 0.3V to 2.0V

- Low Iq: 75uA in DCM mode

- 94% peak efficiency

- Output voltage remote sensing

- ±0.5% system accuracy

- I<sup>2</sup>C and SPI protocol

- Independent dynamic voltage scaling (DVS) for each output

- Programmable frequency from 2MHz to 6MHz

- Full protection features: OVP, UVP, OCP, OTP

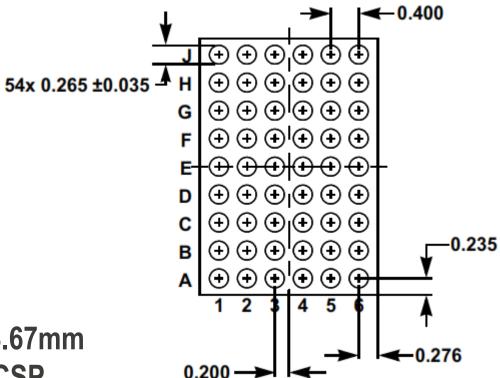

- 2.55mm x 3.67mm 54-ball WLCSP with 0.4mm ball pitch

#### **ISL91302B PACKAGE INFORMATION**

- 2.55mm x 3.67mm

- 54-ball WLCSP

- 0.4mm pitch

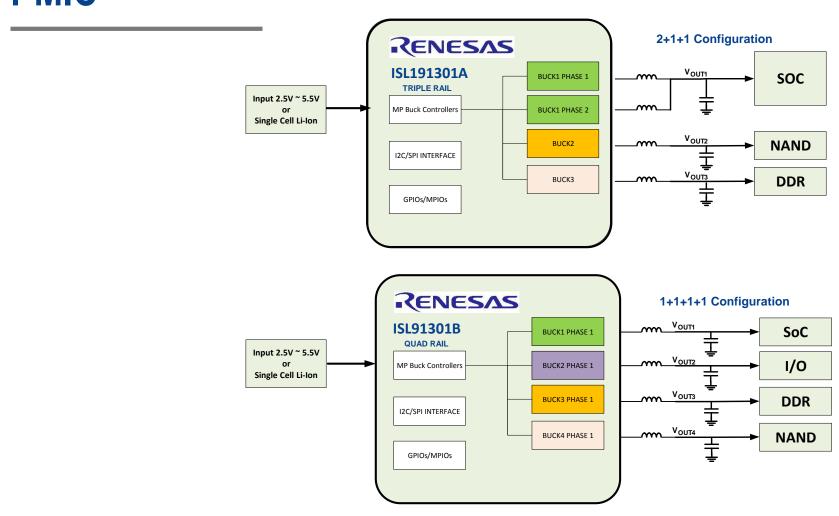

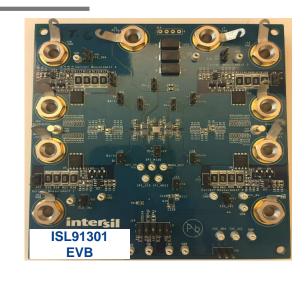

# ISL91301A/B: MULTI-OUTPUT MULTI-PHASE BUCK PMIC

# ISL91301A/B: MULTI-OUTPUT MULTI-PHASE BUCK PMIC

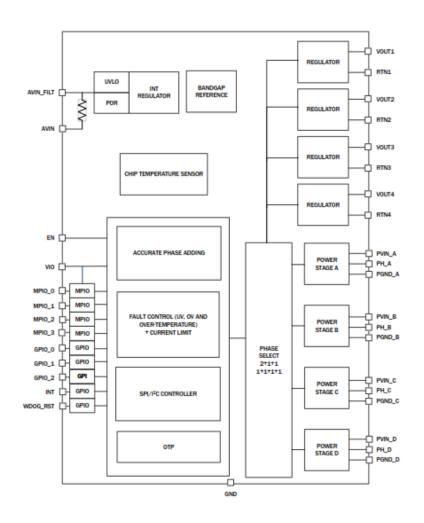

#### ISL91301A/B

- Supported output configurations

- Dual phase (ISL91301A): 2+1+1, Max output: 8A+4A+4A

- Single phase (ISL91301B): 1+1+1+1, Max output: 4A+4A+4A+4A

- 2.5V to 5.5V supply voltage

- Programmable output from 0.3V to 2.0V

- Low Iq: 62uA in low power mode

- 94% peak efficiency

- Output voltage remote sensing

- ±0.7% system accuracy

- I<sup>2</sup>C and SPI protocol

- Independent dynamic voltage scaling (DVS) for each output

- Programmable frequency from 2MHz to 6MHz

- Full protection features: OVP, UVP, OCP, OTP

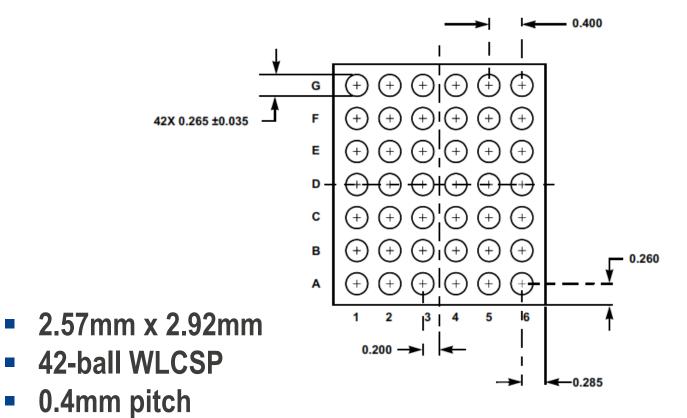

- 2.57mm x 2.92mm 42-ball WLCSP with 0.4mm ball pitch

#### **ISL91301A/B PACKAGE INFORMATION**

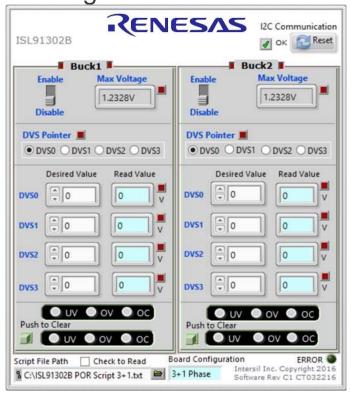

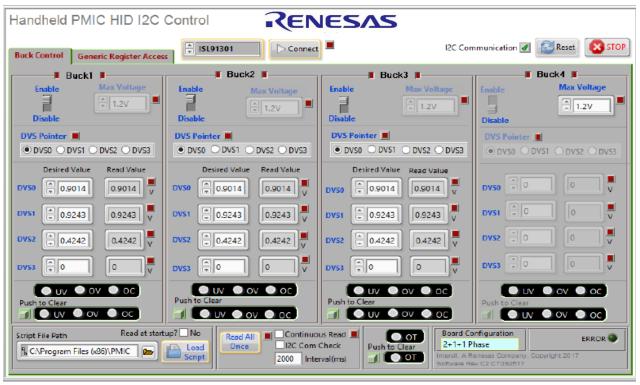

#### **DESIGN IN SUPPORT TOOLS**

#### **ISL91302B COLLATERAL**

#### **Documentation**

- ISL91302B datasheet

- EVB User's Guide

#### **Evaluation Board**

- ISL91302B22-EVZ (for 2+2 configuration)

- ISL91302B31-EVZ (for 3+1 configuration)

- ISL91302B40-EVZ (for 4+0 configuration)

#### **Online Support Portal**

- Online FAQs database

- https://www.intersil.com/en/products/power-management/pmic/integrated-fet-regulators/ISL91302B.html#resources

#### **Ordering Information**

Samples available

P/N: ISL91302BIIZ-T

Reel

3000 Piece/Reel

1K Price: \$3.90

#### ISL91301A AND ISL91301B COLLATERAL

#### **Documentation**

ISL91301A/B datasheet

#### **Evaluation Board**

- ISL91301AII-H-EV1Z (for 2+1+1 4A/phase configuration)

- ISL91301AII-L-EV1Z (for 2+1+1 3A/phase configuration)

- ISL91301BII-H-EV1Z (for 1+1+1+1 4A/phase configuration)

- ISL91301BII-L-EV1Z (for 1+1+1+1 3A/phase configuration)

#### Online Support Portal

- Online FAQs database

- https://www.intersil.com/en/products/power-management/pmic/integrated-fet-regulators/ISL91301.html#resources

#### **Ordering Information**

Samples available

P/N: ISL91301AIIZ-T Reel 3000 Piece/Reel 1K Price: \$3.12

P/N: ISL91301BIIZ-T Reel 3000 Piece/Reel 1K Price: \$3.12

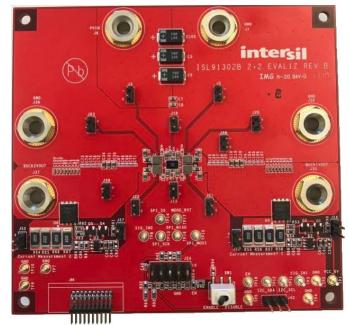

#### **ISL91302B DEMO KIT EVALUATION BOARD**

| <b>EVB Part Number</b> | Description                                        |

|------------------------|----------------------------------------------------|

| ISL91302B22-EVZ        | ISL91302B EVB : 2+2, Max Output Current: 10A + 10A |

| ISL91302B31-EVZ        | ISL91302B EVB : 3+1, Max Output Current: 15A + 5A  |

| ISL91302B40-EVZ        | ISL91302B EVB: 4+0, Max Output Current: 20A        |

#### ISL91301A/B DEMO KIT EVALUATION BOARDS

| <b>EVB Part Number</b> | Description                                                   |

|------------------------|---------------------------------------------------------------|

| ISL91301AII-H-EV1Z     | ISL91301A 4A/Phase EVB: 2+1+1, Max Output Current: 8A+4A+4A   |

| ISL91301AII-L-EV1Z     | ISL91301A 3A/Phase EVB: 2+1+1, Max Output Current: 6A+3A+3A   |

| ISL91301BII-H-EV1Z     | ISL91301B 4A/Phase EVB: 1+1+1+1, Max Output Current: 4A+4A+4A |

| ISL91301BII-L-EV1Z     | ISL91301B 3A/Phase EVB: 1+1+1+1, Max Output Current: 3A+3A+3A |

#### **MULTI-PHASE BUCK PMIC DEMO KITS**

Complete demo kit for multi-phase buck, including EVBs, customer GUI and dongle

ISL91302B & ISL91301A/B Customer GUIs

## DESIGN IN SUPPORT: OPTIMIZED TUNING FOR THE BEST PERFORMANCE

- Multi-phase buck products have more than 700 registers

- To ensure each design is getting best performance:

- Part has been loaded with default register values → starting point

- Registers can be tuned for the best efficiency/transient performance for various L/Cout combinations

- System-level simulation model is provided for performance verification

| ADDRESS | REGISTER           | ADDRESS | REGISTER               | ADDRESS | REGISTER         |

|---------|--------------------|---------|------------------------|---------|------------------|

| 0x01    | IO_CHIPNAME        | 0x30    | ADC_AUXOMSB            | 0x80    | BUCK1_EN_DLY     |

| 0x02    | IO_CHIPVERSION     | 0x31    | ADC_AUXOLSB            | 0x81    | BUCK1_SHUTDN_DLY |

| 0x0A    | IO_DIEID3          | 0x32    | ADC_AUX1MSB            | 0x85    | BUCK2_DCM        |

| 0x0B    | IO_DIEID2          | 0x33    | ADC_AUX1LSB            | 0x89    | BUCK2_CFG0       |

| OxOC    | IO_DIEID1          | 0x42    | IO_I2CCFG              | 0x8A    | BUCK2_PROTCFG    |

| 0x0D    | IO_DIEIDO          | 0043    | IO_SPICEG              | 0x8E    | BUCK2_DVS0CFG1   |

| 0x0E    | OTP_VERSION        | 0x44    | IO_MODECTRL            | 0x8F    | BUCK2_DVS0CFG0   |

| 0x0F    | IO_SOFTRESET       | 0x45    | IO_RSTDVS              | 0x90    | BUCK2_DVS1CFG1   |

| 0x10    | CHIPSTATE          | 0x46    | IO_PINMODE             | 0x91    | BUCK2_DVS1CFG0   |

| 0x11    | CHIPSTATE_DCMPGOOD | 0x58    | FLT_TEMPWARN           | 0x92    | BUCK2_DV52CFG1   |

| 0x13    | FLT_RECORDTEMP     | 0x59    | FLT_TEMPSHUTDN         | 0x93    | BUCK2_DVS2CFG0   |

| 0x14    | FLT_RECORDBUCK1    | 0x5A    | FLT_TEMPHYS            | 0x94    | BUCK2_DVS3CFG1   |

| 0x15    | FLT_RECORDBUCK2    | 0x5B    | FLT_BUCK1_ISENSEWARN   | 0x95    | BUCK2_DVS3CFG0   |

| 0x16    | ADC_SAMPLEOMSB     | 0x5C    | FLT_BUCK2_ISENSEWARN   | 0x96    | BUCK2_VOUTMAXMSB |

| 0x17    | ADC_SAMPLEOLSB     | 0x5D    | FLT_BUCK1_ISENSESHUTDN | 0x97    | BUCK2_VOUTMAXLSB |

| 0x18    | ADC_SAMPLE1PH1MSB  | 0x5E    | FLT_BUCK2_ISENSESHUTDN | 0x98    | BUCK2_DVSCFG     |

| 0x19    | ADC_SAMPLE1PH1LSB  | 0x60    | FLT_MASKTEMP           | 0x99    | BUCK2_DVSSEL     |

| 0x1A    | ADC_SAMPLE1PH2MSB  | 0x61    | FLT_MASKBUCK1          | 0x9A    | BUCK2_RSPCFG1    |

| 0x1B    | ADC_SAMPLE1PH2LSB  | 0x62    | FLT_MASKBUCK2          | 0x9B    | BUCK2_RSPCFG0    |

| 0x10    | ADC_SAMPLE1PH3MSB  | 0x63    | FLT_OT_CTRL            | 0x9C    | BUCK2_EN_DLY     |

| 0x1D    | ADC_SAMPLE1PH3LSB  | 0x64    | FLT_BUCK1_CTRL         | 0x9D    | BUCK2_SHUTDN_DLY |

| 0x1E    | ADC_SAMPLE1PH4MSB  | 0x65    | FLT_BUCK2_CTRL         |         |                  |

| 0x1F    | ADC_SAMPLE1PH4LSB  | 0x69    | BUCK1_DCM              |         |                  |

| 0x20    | ADC_SAMPLE1TMSB    | Ox6D    | BUCK1_CFG0             |         |                  |

| 0x21    | ADC_SAMPLE1TLSB    | 0x6E    | BUCK1_PROTCFG          |         |                  |

| 0x22    | ADC_SAMPLE2MSB     | 0x72    | BUCK1_DVSOCFG1         |         |                  |

| 0x23    | ADC_SAMPLE2LSB     | 0x73    | BUCK1_DVSOCFG0         |         |                  |

| 0x24    | ADC_SAMPLE3MSB     | 0x74    | BUCK1_DV51CFG1         |         |                  |

| 0x25    | ADC_SAMPLE3LSB     | 0x75    | BUCK1_DV51CFG0         |         |                  |

Register Address Map

ADC\_SAMPLE4PH1MSB

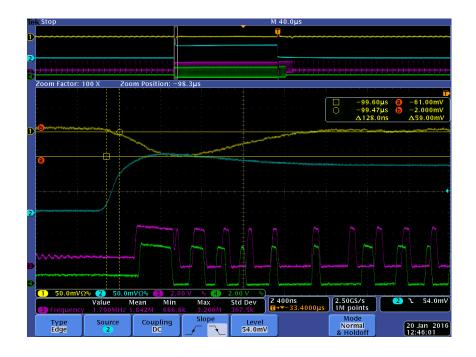

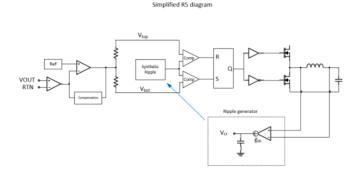

#### **R5 MODULATION TECHNOLOGY INFORMATION**

Home > All Products > Power Management > R5™ Technology

#### **R5 Modulation Technology**

Rapid Robust Ripple Regulator

Reduce board footprint and BOM costs with Intersil's R5™ Technology.

Intersil's R5 Controller Technology is a proprietary modulation technique that offers the fastest response to changing output load conditions. R5 is the next evolution of our unique current-mode hysteretic controller with improved bandwidth and lower Iq than previous implementations.

Using R5 results in much smaller output voltage overshoot and undershoot, resulting in a lower output capacitance. As a result, the board footprint and BOM cost can be reduced significantly.

#### **Key Features:**

- . Best-in-class transient performance

- Stable operating frequency in steady-state with variable duty cycle and frequency in response to load transient

- \* Automatic Phase Adding/Shedding with efficiency optimization algorithm

- \* Seamless, natural transition between PWM and PFM

- · Low-Iq in PFM

https://www.intersil.com/en/products/power-management/r5-technology.html

# BIG IDEAS FOR EVERY SPACE Renesas.com